Product Summary

The UPD72042BGT is a microcomputer peripheral LSI device for IEBus protocol control. The UPD72042BGT performs all the processing required for layers 1 and 2 of the IEBus. The UPD72042BGT incorporates large transmission and reception buffers, allowing the microcomputer to perform IEBus operations without interruption. The UPD72042BGT also contains an IEBus driver and receiver, allowing them to directly connected to the bus directly.

Parametrics

UPD72042BGT absolute maximum ratings: (1) Supply voltage VDD, AVDD: -0.5V to 7.0V | VDD-AVDD | < 0.5 V; (2) Input voltage for logic section VI: -0.5V to VDD +0.3V; (3) Output voltage for logic section Vo: -0.5V to VDD +0.3V; (4) Bus input voltage VBI: -0.5V to +6.0V; (5) Bus output voltage VBO: -0.5V to +6.0V; (6) Operating ambient temperature TA: -40 to +85°C: (7) Storage temperature Tstg: -65°C to +150°C.

Features

UPD72042BGT features: (1) Control of layers 1 and 2 of the IEBus protocol; (2) Support of a multi-master scheme; (3) Broadcast function; (4) Two communication modes having different transmission speeds can be selected; (5) transmission speeds can be selected; (6) Program crashes can be detected by means of a watchdog timer; (7) Low power consumption (standby mode): 50μA (max) ; (8) Oscillator frequency (fX): 6MHz, 6.29MHz; (9) frequency accuracy: ±1.5%; (10) Operating voltage: 5V, ±10%.

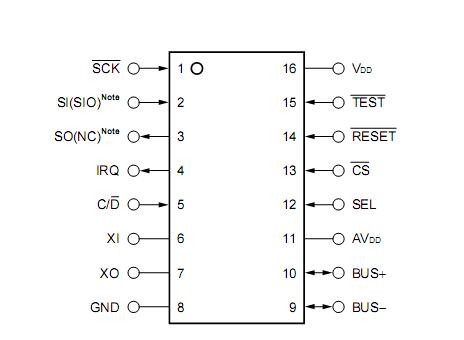

Diagrams

(China (Mainland))

(China (Mainland))